# Auto Generation Is the Key to Rapid Integration to UPF-like UPVM Libraries for Unified Power Verification

Gopi Srinivas Deepala, Lakshay Miglani, Himanshu Vishwakarma and Priyanka Gharat

EasyChair preprints are intended for rapid dissemination of research results and are integrated with the rest of EasyChair.

October 8, 2024

# Auto Generation is the key to rapid integration to UPF-like UPVM libraries for Unified Power Verification

Gopi Srinivas Deepala, Engineer - VLSI Design, Silicon Interfaces, Mumbai, India (gopi@siliconinterfaces.com)

Lakshya Miglani, Engineer - VLSI Design, Silicon Interfaces, Mumbai, India (lakshya@siliconinterfaces.com)

Himanshu Vishwakarma, Engineer - VLSI Design, Silicon Interfaces, Mumbai, India (himvish@siliconinterfaces.com)

Priyanka Gharat, India (gharatpriyanka0@gmail.com)

Abstract- This paper illustrates the powerful automation resource, a python based tool, smoothly combines UPF power strategies with UPVM class libraries. UPVM, the evolving open source standard for Unified Power Verification Methodology<sup>TM</sup>, serves as a bridge between UVM and UPF. This automation offers a fresh perspective on generating UPF constructs, facilitating a seamless journey from the RTL to GLS and GDSII stages for Design under Test (DUTs) with a focus on low-power features. This versatile utility simplifies intricate tasks such as managing power domains, organizing hierarchical sets, creating supply ports, connecting them, handling state transitions, and implementing comprehensive power strategies to bridging the gap between UPF and UVM methodologies, overcoming challenges related to power management during verification. Additionally, it optimizes the translation of power goals from RTL to GLS/GDSII, ensuring strict compliance with low-power requirements. Through its holistic and integrated approach, this tactic aims to revolutionize low-power semiconductor design practices, leading to improved power efficiency, reduced errors, and smoother transitions throughout the various stages of design development.

Keywords—Unified Power Verification Methodology (UPVM), Unified Power Format (UPF), Universal Verification Methodology (UVM), Automation, Power Management, Power Verification.

#### I. INTRODUCTION

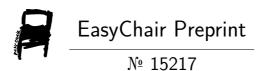

Recent advancements in semiconductor design have seen the active integration of power verification methodologies. Notably, the combination of Unified Power Format (UPF) and Universal Verification Methodology (UVM) techniques has been explored to address power management challenges during the verification phase as shown in Figure I and Ref 3 and Ref 4 as given in the Reference Section.

Figure I: Unified Power Verification Methodology (UPVM) - Bridge

A significant innovation in this area is the development of an automation named aUPVM.py. aUPVM is a Python-based tool, which makes it simple for the Designer to integrate Low Power methodologies and strategies to Design Under Test (DUT) at an early stage and integrate with SystemVerilog Verification using previously developed myUPVM templates and UPVM libraries, like upf\_version, set\_design\_top, set\_scope, set\_directory, create\_power\_domain, create\_ports, Etc. (UPVM, the evolving open source standard libraries for Unified Power Verification Methodology<sup>TM</sup>, serves as a bridge between UPVM and UPF, previously developed).

The automation's capabilities are further enhanced by integrating the low-power strategies developed for myUPVM templates which are extensions of the UPVM libraries. By leveraging SystemVerilog classes and packages, the automation implements UPF-likeSystemVerilog files based on low-power strategies defined in lpdut files. This ensures the effective translation of low-power strategies into the design, aligning with industry standards and regulations.

Following the generation of the low-power UPF-like file and integrating the same to myUPVM, power validation is conducted during the UPVM verification phases. In the validation phase (part of UPVM libraries), the generated power strategies shall be validated with mapped library components for violations and conflicts. This enables comprehensive power verification, ensuring the accuracy and reliability of semiconductor designs.

### II. AUTOMATION FOR STREAMLINING THE UPF STRATEGIES

This aUPVM represents a major advancement in automating the creation of UPF-like strategies for semiconductor design. Its primary goal is to streamline the generation of intermediate file formats which can be integrated into myUPVM template files by providing developers with an intuitive interface.

In the beginning, the automation begins by prompting developers to initialize the file with the correct UPF version being used (for this paper version 2.0) as shown in Figure II.

| ******   |         | *****        | *****               |

|----------|---------|--------------|---------------------|

| **** aUP | VM Prov | ided by Sili | con Interfaces **** |

| ******   |         | ******       | *****               |

|          |         |              |                     |

| Provide  | the UPF | version : 2  | .0                  |

Figure II: aUPVM automation

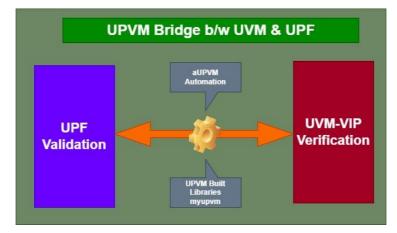

The tool next facilitates directory selection, by navigating through the directories and selecting the specific directory which contains the design files. Use the provided commands to move up (goto), and do (goback) across directories as shown in Figure III.

Figure III: Directory Selection Procedure

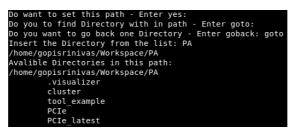

It integrates with the design and then it displays the design hierarchy, which will reduce the complexity to identify the Design hierarchy which makes it easy to select the top module to developers as shown in Figure IV.

A standout feature of automation is its ability to create power domains based on the design hierarchy. When creating power domains, the aUPVM automation prompts designers to specify which elements within the hierarchy require power domains. It then presents the module hierarchy for each module to assist in the selection process as shown in Figure V.

| Available modules:      |

|-------------------------|

| ocie_rx                 |

| /pcie_rx/tsl            |

| /pcie_rx/phy_rx         |

| /pcie_rx/phy_rx/us      |

| /pcie_rx/phy_rx/cdr     |

| /pcie rx/phy rx/cdr/ba  |

| /pcie rx/phy rx/cdr/pll |

| /pcie_rx/phy_rx/cdr/eb  |

| /pcie_rx/phy_rx/cdr/s2p |

| /pcie_rx/phy_rx/d0      |

| /pcie_rx/phy_rx/pf      |

| /pcie_rx/dll            |

| ocie tx                 |

| /pcie tx/phy tx         |

| /pcie_tx/phy_tx/pf_tx   |

| /pcie_tx/phy_tx/strip   |

| /pcie_tx/phy_tx/p2s     |

| /pcie_tx/tlp            |

| /pcie_tx/dlp            |

|                         |

Figure IV: Design Hierarchy

Figure V: Module Hierarchy for selecting the Power Domain elements

By integrating with existing UPF files, the automation aligns power domain elements with the current design structure, ensuring compatibility before adding the legacy UPF file. This enhances the reuse, accuracy, and efficiency of power domain creation, crucial for effective power management in semiconductor designs.

One of the automation's key features is its interactive approach, which collects designer requirements for specific UPF strategies. Through a series of prompts and options, the automation skillfully guides designers through the necessary steps to develop UPF-like strategies that align with their design goals.

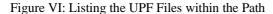

During the selection of the existing UPF file once you have reached the desired directory, confirm your selection to begin the existing UPF File from the listed as shown in Figure VI.

When incorporating a UPF-like intermediate file, to facilitate hierarchical incorporation of legacy designs, the automation process will first read the power domains defined in the UPF file. It will then compare these domains with the current design hierarchy. The UPF file will only be added if there is a match between the power domains in the UPF file and the elements in the design hierarchy as shown in Figure VII. If a mismatch is detected, an error will be generated, indicating that the UPF file addition has failed. Therefore, it is crucial to ensure that the power domains specified in the UPF file align with the elements in the current design hierarchy before proceeding as shown in Figure VIII.

| Do want to set this path - Enter yes:<br>Do you to find Directory with in path - Enter goto:<br>Do you want to go back one Directory - Enter goback: yes<br>/home/gopisrinivas/Workspace/PA/PCIe<br>pcie_upf1.upf<br>pcie.upf | Enter the file Name from the list: pcie_latestl.upf<br>Available Power Domain in this file<br>System Verilog Files Found in this Directory<br>Match Found: The Power Domain Elements Present in this Design<br>Element in UPF File: pcie_tx<br>Design Hierarchy: pcie_tx |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| pcie_latest2.upf                                                                                                                                                                                                              | System Verilog Files Found in this Directory                                                                                                                                                                                                                             |  |

| pcie_latest1.upf                                                                                                                                                                                                              | Match Found: The Power Domain Elements Present in this Design                                                                                                                                                                                                            |  |

| pcie_latest.upf                                                                                                                                                                                                               | Element in UPF File: pcie_rx<br>Design Hierarchy: pcie_rx                                                                                                                                                                                                                |  |

| pcie_final.upf                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                          |  |

| pcie_latest3.upf                                                                                                                                                                                                              | System Verilog Files Found in this Directory<br>System Verilog Files Found in this Directory                                                                                                                                                                             |  |

| No more UPF files are Available                                                                                                                                                                                               | System Verilog Files Found in this Directory<br>The Load UPF File Successful                                                                                                                                                                                             |  |

Figure VII: Match Pass Elements Comparison

Figure VIII: Match Fail Elements Comparison

Additionally, the automation facilitates the creation of ports, nets, and supply sets, along with their associated supply sets and logic ports. It establishes connections between logic nets and generates power switches and states. These features contribute to the comprehensive implementation of low-power strategies in UPF files for energy efficiency and reducing power consumption in semiconductor designs.

The automation provides designers with a streamlined approach to specifying their required strategies for UPFlike intermediate file creation. Designers are presented with options, including tasks such as creating nets, logic nets, and ports, as well as establishing connections between these elements. Additionally, designers can define supply sets and associated supply sets, configure power switches and states, and incorporate state and logic expressions into their UPF-like intermediate files. The automation also supports the integration of level shifters, isolation cells, and retention cells into the power management scheme. This allows designers to maintain control over these strategies, tailoring the UPF-like intermediate file generation process to meet their specific design requirements. Once designers have made their selections, the automation consolidates all the output into a lpdut file. This lpdut file serves as the foundation for integrating with myUPVM templates (which are leveraging UVPM libraries as shown in Figure XI)and then generating the UPF file to ensure the effective implementation of the specified power management strategies as shown in Figure IX.

| [ | upf_version]:2.0                                                              |

|---|-------------------------------------------------------------------------------|

| [ | top]:pcie top                                                                 |

| [ | scope]:pcie top                                                               |

| i | pd]:PD PD PCIE TOP;                                                           |

|   | pd]:PD_PD_PCIE_PHY_CDR;[elements]:pcie_rx/phy_rx/cdr;                         |

|   | pd]:PD_PD_PCIE_RX;[elements]:pcie_rx;[supply]:primary;[supply]:backup;        |

|   | pd]:PD_PD_PCIE_TX;[elements]:pcie_tx;[supply]:primary;[supply]:backup;        |

|   | set dir]:UPF DIR /home/gopisrinivas/Workspace/PA/PCIe latest                  |

|   |                                                                               |

| [ | upf file]:/home/gopisrinivas/Workspace/PA/PCIe/pcie latest1.upf               |

| ī | upf file]:/home/gopisrinivas/Workspace/PA/PCIe/pcie.upf                       |

| I | upf file]:/home/gopisrinivas/Workspace/PA/PCIe/pcie upf1.upf                  |

| I | upf file]:/home/gopisrinivas/Workspace/PA/PCIe/pcie final.upf                 |

| [ | ports]:VDD1;VSS1,VDD2;VSS2                                                    |

| [ | nets]:RX Pwr;[domain]:PD PD PCIE RX                                           |

| [ | nets]:RX_Gnd;[domain]:PD_PD_PCIE_RX                                           |

| [ | nets]:CDR Pwr;[domain]:PD PD PCIE PHY CDR                                     |

| [ | nets]:CDR Gnd;[domain]:PD PD PCIE PHY CDR                                     |

| [ | nets]:TX Pwr;[domain]:PD PD PCIE TX                                           |

|   | connect_net]:RX_Pwr;VDD1,RX_Gnd;VSS1,CDR_Pwr;VDD2,CDR_Gnd;VSS2                |

|   | create_supply_sets]:CDR_SS;[function]:power,CDR_Pwr;[function]:ground,CDR_Gnd |

| [ | associate supply set]:CDR SS;[handle]:PD PD PCIE PHY CDR.primary              |

Figure IX: lpdut File outcome of Automation

#### III. UTILIZING THE UPVM LIBRARIES TO INTEGRATE AND GENERATE UPF FILES

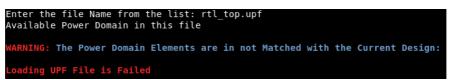

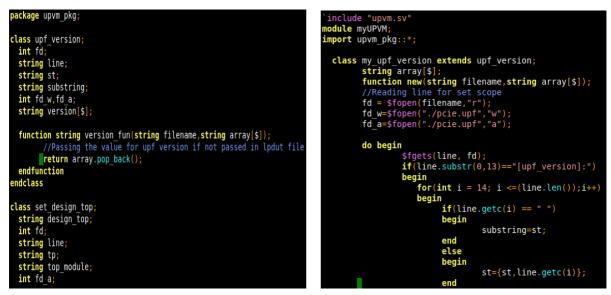

After generating the lpdut file using the Python automation, utilizing the UPVM libraries to extract the lpdut file into the UPF File, and integrating with Low Power Strategies for the Power Validation at the earlier stage of the UVM verification, these libraries developed using SystemVerilog packages as shown in Figure X, are specifically designed to provide the utilities and functionalities necessary to integrate with the power strategies for the Low Power Validation. The myupvm.sv file integrates these built-in UPVM libraries, facilitating the seamless construction of UPF files as shown in Figure XI.

Designers can be permitted to execute the myupvm.sv file uses the UPVM libraries to interpret the lpdut file and generate the corresponding UPF file. This process ensures the efficient translation of the low-power strategies outlined in the lpdut file into UPF files, aligning with industry standards and regulations.

Moreover, the UPVM libraries are crucial in accessing UPVM strategies within the UVM-like testbench and Scoreboard. These libraries are integrated into the UVM test-bench codebase, enabling access to UPVM strategies during UPF file creation and Verification. They are also incorporated into the Scoreboard to facilitate validation of methodologies and strategies. This comprehensive validation ensures the ability of the power management strategies to validate Low Power design within the UVM environment.

Figure X: UPVM Libraries Package

Figure XI: myUPVM Template (myupvm.sv)

IV. APPLICATIONS

The primary function of the aUPVM tool is to facilitate UPVM generation, offering several valuable applications to the semiconductor industry:

- 1. **Standardized Power Domain Management:** UPVM ensures consistency and standardization in power domain management practices.

- 2. **Low-Power Design Implementation:** The tool enables the implementation of low-power design strategies, promoting energy efficiency in semiconductor devices.

- 3. **Streamlined Design Workflows:**aUPVM contributes to smoother design workflows, reducing complexity and optimizing resource allocation.

- 4. **Enhanced Power Verification:** UPVM-based verification methods enhance the accuracy and effectiveness of power verification processes.

- 5. **Efficient UPF File Generation:**aUPVM streamlines the process of generating UPF files, enhancing efficiency in downstream semiconductor design post-synthesis and physical layouts.

UPVM-based low-power verification provides significant advantages, such as cost reduction and faster timeto-market, by integrating low-power validation at an early stage in the design process alongside functional verification. These UPVM-based designs are set to play critical roles across various industries.

- 1. **Mobile Devices:** UPVM-based devices can expedite the release of smartphones and tablets, potentially advancing them ahead of current technology by half a generation.

- 2. **Automotive Electronics:** UPVM-based processors can minimize the launch time gap for advanced vehicle technologies reliant on semiconductor chips.

- 3. **Medical Devices:** Time-efficient semiconductor components enabled by UPVM can expedite the development of medical devices, potentially improving their timely deployment and impact on saving lives.

- 4. **Data Centers:** UPVM-based devices used in data centers can be delivered ahead of schedule, enhancing data processing capabilities and efficiency in managing vast amounts of data.

## V. RESULT

The aUPVM.py tool was tested on a low-power PCIe design, using automation to integrate Low Power methodologies and strategies in the Design & Verification phase, using UVM-like methodologies, and validating the same in the Scoreboards as shown in Figure XII and then generating UPF constructs as shown in Figure XIII. The results demonstrated a significant reduction in the complexity of writing UPF code, with noticeable simplification. Moreover, the seamless integration with UPVM libraries facilitated early-stage power validation. Additionally, the tool's ability to generate UPF files allowed for seamless integration with standard tools for GLS and GDSII validation.

| <pre>class scoreboard;<br/>my_upf_version upf_ver;<br/>my_hirearchy_c my_hy;<br/>my_set_design_top msdpl1;<br/>my_set_scope ssp;<br/>my_create_power_domain my_crt_pd;<br/>my_create_supply_port my_crt_sp;<br/>my_create_supply_net my_crt_sp;<br/>my_create_supply_net my_crt_sp;<br/>my_create_logic_net_c_my_crt_gdsn;<br/>my_add_port_state my_aps;<br/>my_add_port_state my_aps;<br/>my_set_retention_c_my_sit;<br/>my_set_level_shifter_c_my_sls;<br/>my_supply_sets my_ss;<br/>my_load_upf_c_my_ldupf;<br/>my_lassociat_ss;<br/>my_load_pst_st_my_ast_c_my_asociat_ss;</pre> | <pre>create_power_domain PD_PCIE_TOP<br/>create_power_domain PD_TX -elements { pcie_tx } \<br/>-supply {primary} \<br/>-supply {backup} \<br/>create_power_domain PD_PX -elements { pcie_rx } \<br/>-supply {backup} \<br/>create_power_domain PD_TX -elements { pcie_tx/phy_tx/pll }<br/>create_power_domain PD_TXPLL -elements { pcie_rx/phy }<br/>create_power_domain PD_CNR -elements { pcie_rx/phy/cdr }<br/>create_supply_net Pwr -domain PD_TX<br/>create_supply_net Gnd -domain PD_TX<br/>create_supply_net GndTxpll -domain PD_TXPLL<br/>create_supply_net GndTxpll -domain PD_TXPLL<br/>create_supply_net Gnd -domain PD_PHY<br/>create_supply_net Gnd -domain PD_PHY<br/>create_supply_net Gnd -domain PD_PHY<br/>create_supply_net Gnd -domain PD_PHY<br/>create_supply_net Gnd -domain PD_CDR<br/>create_supply_net Gnd -domain PD_CDR<br/>create_supply_net Gnd -domain PD_HY<br/>connect_supply_net Fwr -ports {VDD1}<br/>connect_supply_net Fwr -ports {VD2}<br/>connect_supply_net PwrTxpll -ports {VD2}<br/>connect_supply_net PwrTxpll -ports {VD2}<br/>add_port_state PST1 \</pre> |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <pre>my_associate_supply_set_c_my_associat_ss;<br/>my_add_power_state_c_my_apwrs;<br/>my_set_dir_c_my_sd;</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

Figure XII: UPVM Scoreboard for access Validate the low-power strategies

Figure XIII: UPF File Generated by myUPVM template

#### VI. CONCLUSION

This automation and integration to UPVM libraries has performance improvement and ease of use and is crucial for creating and verifying DUT with Low Power methodologies and strategies files early-stage in semiconductor designs' power management. By incorporating UPF strategies into the SystemVerilog UPVM test bench and Scoreboard, comprehensive verification (the lower power strategies are in SystemVerilog so the cause and effects of power management can be verified early stage in the design phase) and validation of power management strategies are achieved, facilitating early-stage Unified Power Verification. The advancement of the aUPVM & myUPVM template is there is no longer required to learn the UPF constraints to build the low-power design and the verification engineer also can generate the low-power design for DUT. Additionally, it simplifies the process of UPF file creation and enables thorough examination and debugging of low-power features, thereby contributing significantly to the overall success of semiconductor design projects.

#### REFERENCES

- [1] UVM Community (accellera.org) <u>https://accellera.org/community/uvm</u>.

- [2] Guide to changes in IEEE 1801-2013 (UPF 2.1) (techdesignforums.com)

- [3] Low Power Classes as extension to UVM Package Library 59th Design Automation Conference 2022

- [4] Low Power Extension in UVM Power Management DVCon India 2022

- [5] Verification Methodology Manual for Low Power https://www.synopsys.com/company/resources/synopsys-press/vmm-low-power.html

- [6] Arm Cortex-A53 MPCore Processor Technical Reference Manual r0p4